How to get higher power output with lower power input?

[Guide]If you want to go further, gate driver features such as delay matching can effectively double the drive current capability. Delay matching refers to the matching of internal propagation delays between two channels, which can be achieved by parallel output of dual-channel gate drivers or by bundling two channels together. For example, TI’s UCC27524A has an extremely accurate 1ns (typical) delay matching, which can increase the drive current from 5A to 10A.

In today’s world, designers seem to never stop pursuing higher efficiency. We hope to get higher power output with lower power input! Higher system efficiency requires team effort, which includes (but is not limited to) higher performance gate drivers, controllers and new wide bandgap technologies.

Especially high-current gate drivers, which can help improve overall system efficiency by reducing switching losses. When the FET switch is turned on or off, switching losses occur. In order to turn on the FET, the charge from the gate capacitance must exceed the threshold voltage. The driving current of the gate driver can contribute to the charging of the gate capacitance. The higher the driving current capability, the faster the charging and discharging speed of the capacitor. The ability to draw a large amount of charge can reduce power loss and distortion. (Conduction loss is another type of FET switching loss. The conduction loss depends on the internal resistance or the RDS(on) value of the FET. The FET will also dissipate power as current passes.)

In other words, the goal is to reduce the switching transition time that requires high-frequency power conversion in the system. The gate driver specifications that highlight this type of performance are rise and fall times. See Figure 1.

Figure 1: Typical rise and fall time diagram

If you want to go further, gate driver features such as delay matching can effectively double the drive current capability. Delay matching refers to the matching of internal propagation delays between two channels, which can be achieved by parallel output of dual-channel gate drivers or by bundling two channels together. For example, TI’s UCC27524A has an extremely accurate 1ns (typical) delay matching, which can increase the drive current from 5A to 10A.

Figure 2 shows an example of UCC27524A channel A and channel B combined in one driver. The INA and INB inputs and OUTA and OUTB are connected in series respectively. The parallel combination is controlled by a signal.

Figure 2: Series output UCC27524A to double the dual drive current capability

One of the results brought about by the increase in system efficiency is the increase in power density. In applications such as power factor correction (PFC) and synchronous rectifier blocks, DC/DC modules and solar inverters of isolated power supplies, designers need to be restricted to achieve the same output power in the same size (or smaller). Therefore, the demand for higher power density has become a trend.

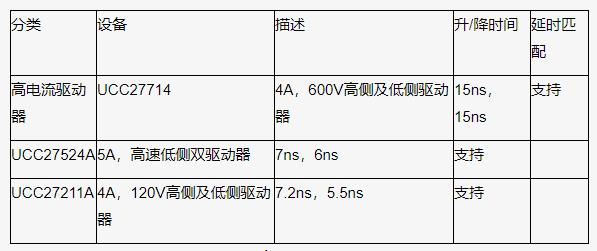

TI’s product portfolio includes gate drivers with high current, fast rise and fall times, and delay matching. See Table 1.

Table 1: High current gate driver

(Source: China Power Grid)

The Links: 6MBI15F-120 FP25R12KT3 THE IC INFO